Overview

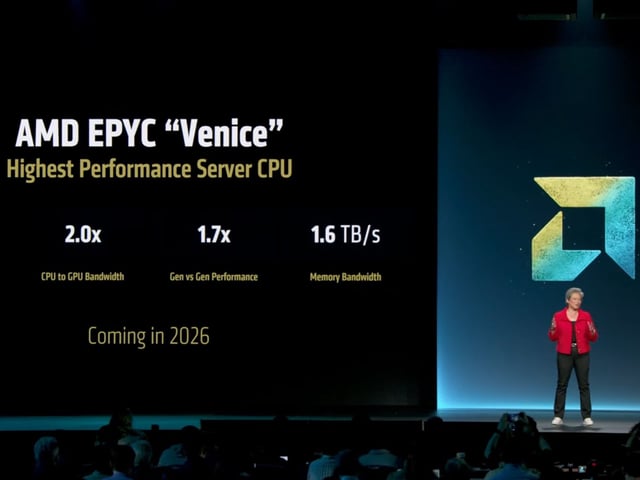

- The EPYC ‘Venice’ processor boosts per-socket memory bandwidth from 614 GB/s to 1.6 TB/s.

- It is expected to support PCIe Gen 6 connectivity with up to 128 lanes to underpin high-speed CPU-GPU transfers.

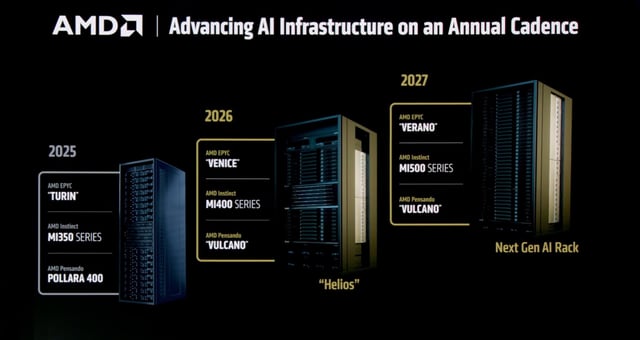

- New SP7, SP8 form factors will allow AMD to increase CCD counts per package, add more memory channels.

- AMD plans to follow Venice with EPYC ‘Verano’ CPUs and Instinct MI500 GPUs in 2027.

- Venice, Instinct MI400 GPUs and Vulcano FPGAs will be integrated into AMD’s Helios data center rack for AI workloads in 2026.